Introduction to the Xilinx platform Studio (XPS)のチュートリアルについて手順を載せる. このチュートリアルでは,LSFR(Linear Feedback Shift Register)を用いた擬似乱数生成器を実装する.擬似乱数器はすでに設計済みのものが提供されており,XPSを用いてFPGA上に実装する.

XPS †

必要なもの

- WARPv3ボード

- 静電気対策(リストバンド等)

- 外付けのUSB JTAGケーブルとマイクロUSBケーブル

- ISE System Edition

- PuTTY等のターミナルエミュレータ

- SDKのチュートリアルを終わらせていること

入力 †

- User I/O Pushbutton Port:WARPについているプッシュボタン

- Capture Period Register:MicroBlaze・・・LSFR(Linear Feedback Shift Register)を制御する.

出力 †

- Left/Right Hex Display Ports:User I/Oについている16進数表記のディスプレイ

- Red/Green LED Ports:User I/Oについている赤と緑のLED

- Captured output Register: 現在のLFSRの値を読める.

手順 †

- WARP v3 Template Projectをダウンロードして解凍する.

# パスの間にスペースをいれない.

- pcoreをダウンロードして先ほどダウンロードしたプロジェクトフォルダ\pcoresの直下に解凍する.

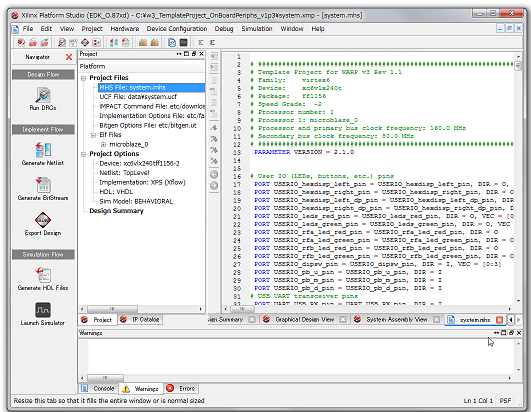

- XPSを起動 > スタートメニュー > "Open project"をクリック > ダウンロードしたフォルダ内にあるsystem.xpsを選択 > "open"をクリック

# 初めてXPSを開く場合またはWARPリポジトリの設定をしていない場合は,設定をする.詳しくはSubversion Repositoryを参照されたい.

- 新しくpcoreとシステムをつなぐため,system.mhsを変更するため,"Project"タブ > "Project Files"の中にあるsystem.mhsをダブルクリック.

- 以下のコードをsysytem.mhsの末尾に書き込む.

BEGIN prng_useriosrc_plbw PARAMETER INSTANCE = prng_useriosrc_plbw_0 PARAMETER HW_VER = 1.02.a PARAMETER C_BASEADDR = 0xc4000000 PARAMETER C_HIGHADDR = 0xc400ffff BUS_INTERFACE SPLB = plb_secondary_80MHz PORT sysgen_clk = clk_80MHz PORT hexdisp_left = LeftHexDisplay PORT hexdisp_right = RightHexDisplay PORT leds_green = GreenLEDs PORT leds_red = RedLEDs PORT pause = UpPushbutton END

- 以下のコードを"BEGIN w3_userio."の"END"の前の行に書き込む

PORT usr_hexdisp_left = LeftHexDisplay PORT usr_hexdisp_right = RightHexDisplay PORT usr_leds_green = GreenLEDs PORT usr_leds_red = RedLEDs PORT usr_pb_u = UpPushbutton

- System Assembly Viewタブを開き,"Bus Interfaces"サブタブを見る.